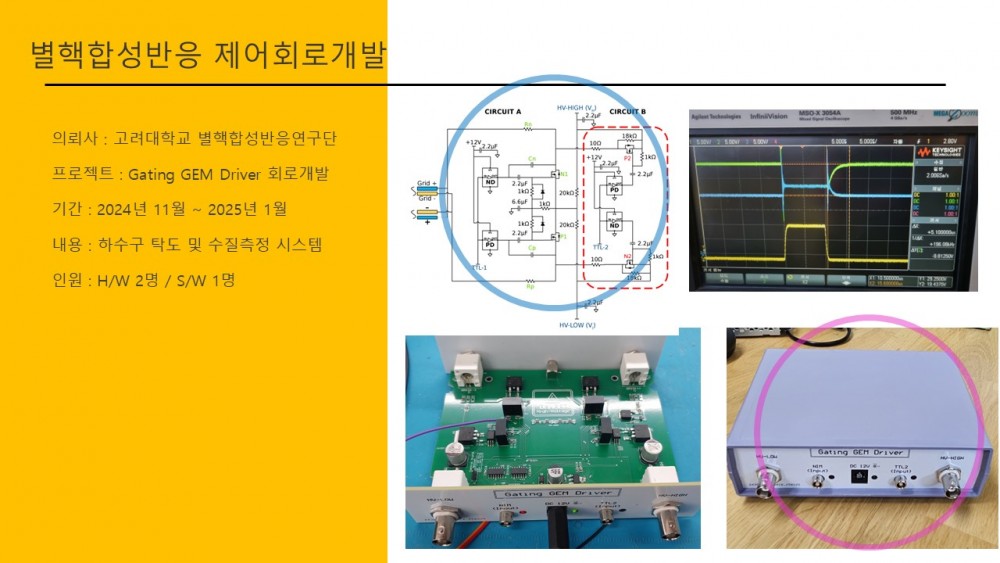

개발 갤러리 고려대학교 별핵합성반응연구단

1. 프로젝트명 : 별핵합성반응 연구용 제어회로개발

2. 개발기간 : 3개월

3. 개발내용 : 회로설계, PCB설계, 펌웨어, PC프로그램 개발

4. 상세 개발 : NIM signal에 따라 전압 상태를 바꾸는 회로를 별핵합성반응 연구용 제어회로를 이용해 전기장을 걸어 전자의 흐름을 직접 컨트롤하고 노이즈가 적은, 1 ㎲ 이하의 시간안에 전압 변화가 되는 회로와 보드개발로 NIM signal이 없을 때는 두 output이 각각 50~30 V의 high level, 20~10 V의 low level을 유지하다가 NIM signal이 들어오면 두 output의 전압을 같

게 만드는 gating 회로입니다.

- 날짜: 26-02-10 14:51

- 조회: 605

LOGIN

LOGIN 주문내역

주문내역 CART(0)

CART(0) 자료실

자료실 고객센터

고객센터